- HBM4e eleva o bus para 2048 bits, mira até 12,8 Gbps/pino e 1,6–2,0 TB/s por pilha.

- Eficiência melhora (≈3,5–5 pJ/bit), com hybrid bonding viabilizando pilhas 16‑hi.

- IA/HPC ganham com menos gargalos; GDDR7 segue mais viável em GPUs de consumo.

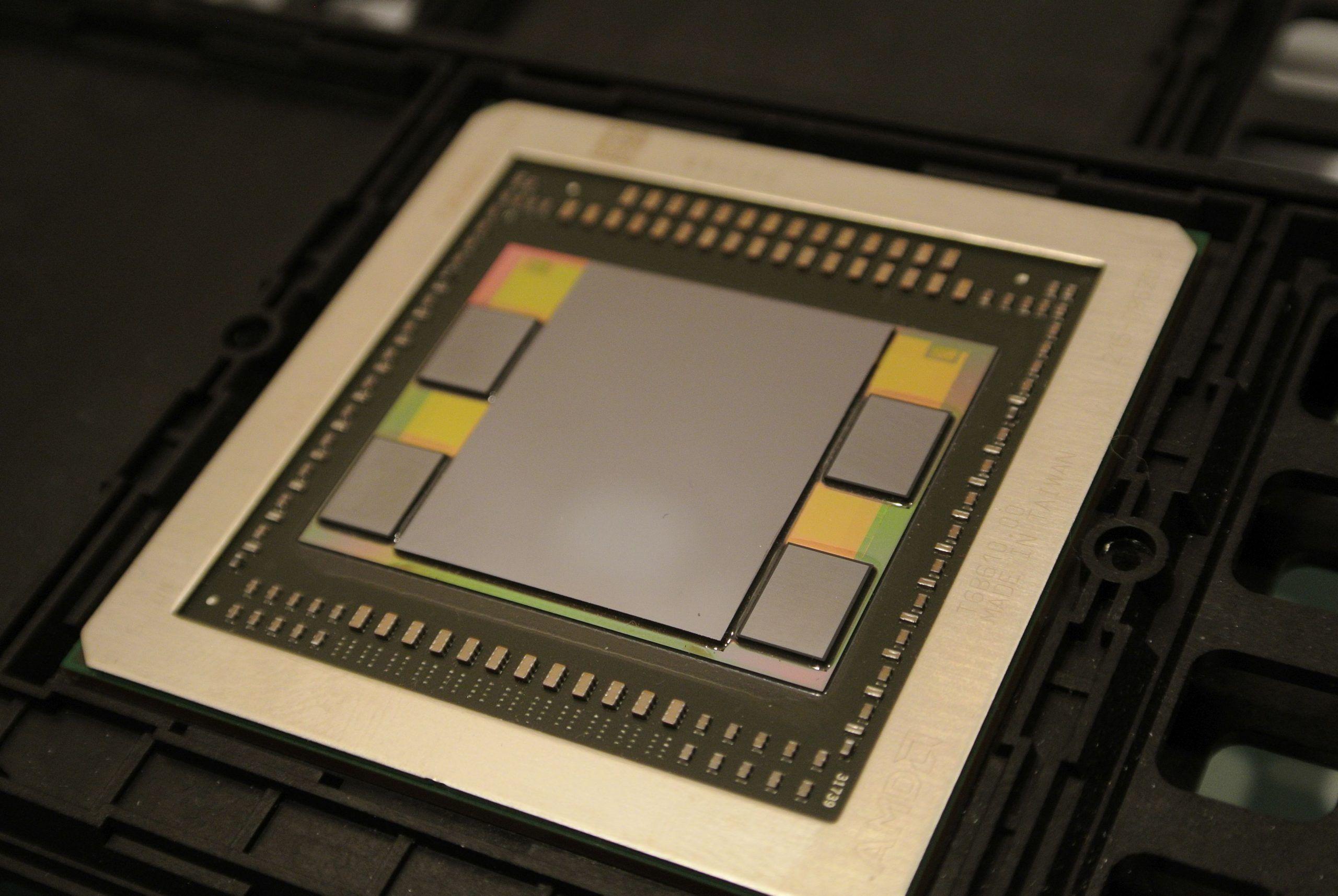

Os projetos de inteligência artificial e computação de alto desempenho estão a devorar dados, e é aí que a memória de alto throughput entra em cena. A HBM (High Bandwidth Memory) tornou-se peça-chave para alimentar GPUs, ASICs e CPUs específicas com um fluxo de dados massivo, reduzindo gargalos que antes eram inevitáveis com DDR ou GDDR tradicionais.

Neste panorama, a próxima evolução, a HBM4e, desponta como um salto relevante sobre a HBM3 e a base do padrão HBM4. Ela promete mais largura de banda por pilha, melhor eficiência energética e novas técnicas de empacotamento 3D, tudo pensado para workloads como LLMs, modelos multimodais e simulações científicas que exigem acesso contínuo à memória.

Tabela comparativa: HBM3 vs HBM4e

Para situar o avanço, vale observar uma síntese lado a lado entre as duas gerações. Os números deixam claro o aumento em bus, taxa por pino, capacidade por pilha e, sobretudo, em eficiência.

| Parâmetro | HBM3 | HBM4e |

|---|---|---|

| Processo DRAM | 1α/1β nm | 1γ nm ou inferior |

| Largura de bus por pilha | 1024 bits | 2048 bits |

| Taxa de dados por pino | Até 6,4 Gbps | Até 12,8 Gbps |

| Largura de banda por pilha | ~819 GB/s | 1,6–2,0 TB/s |

| Tensão de operação | ~1,1 V | ~1,0 V |

| Energia (pJ/bit) | 5–7 pJ/bit | 3,5–5 pJ/bit |

| Nº máx. de camadas DRAM | 12–16 | 16+ (com hybrid bonding) |

| Capacidade por pilha | Até 64 GB | Até 128 GB |

| Tipo de ligação | TSV + micro-bump | Ligação híbrida Cu–Cu |

| Latência relativa | Alta (similar à HBM2e) | Moderadamente menor |

Como ler os “nós” de tecnologia na DRAM

Ao contrário de CPU/GPU, onde o “nm” virou sinônimo de nó de processo, as DRAMs adotam uma nomenclatura alfanumérica (1x, 1y, 1z, 1α, 1β, 1γ, 1δ…) para expressar gerações sucessivas de refinamento; isso acontece porque a célula de memória (transistor + capacitor) não escala linearmente como lógica CMOS.

Manter capacitância útil (~20–30 fF) limita o encolhimento do capacitor, logo, o “nm” não é comparável de forma direta à lógica. Por isso, HBM3 aparece perto de 1α/1β e HBM4e evolui para 1γ e abaixo, refletindo melhorias de densidade, consumo e confiabilidade, sem a obsessão por gate length típica da lógica.

HBM3: arquitetura e pontos de atenção

A terceira geração do padrão JEDEC, a HBM3, manteve o DNA das versões anteriores: pilhas de DRAM interligadas por TSVs sobre um interposer de silício e um bus gigantesco de 1024 bits. Em cenários práticos, cada pilha pode entregar algo como 819 GB/s, com taxas por pino que chegam a 6,4 Gbps.

Uma pilha típica reúne 8 a 16 dies, e a interface física emprega sinais diferenciais de alta integridade para conter jitter e perdas. Esse desenho prioriza throughput massivo, o que atende muito bem GPUs e aceleradores, ainda que a latência não seja dramaticamente reduzida frente às gerações passadas.

Limitações técnicas

- Empacotamento complexo: interposers grandes elevam custos e trazem desafios térmicos difíceis de mitigar.

- Escalabilidade térmica: mais camadas na pilha aumentam a resistência térmica vertical e dificultam a dissipação de calor.

- Yield sob pressão: empilhar múltiplos dies por TSV aumenta a chance de defeitos e pressiona o rendimento de fabricação.

- Latência ainda elevada: a ênfase segue sendo largura de banda, não resposta imediata; em muitos casos, a DDR conserva vantagem de latência.

HBM4e: o que muda em relação à HBM4 e HBM3

A HBM4e (de “extended”) amplia a base técnica da HBM4 do JEDEC. São esperadas taxas até 12,8 Gbps por pino, bus de 2048 bits e 32 canais (64 pseudo-canais), com pilhas variando de 4‑hi a 16‑hi e capacidades por pilha que podem chegar a 128 GB quando combinadas com dies de alta densidade.

Em parâmetros JEDEC para HBM4, fala-se em até 2 TB/s por pilha com 8 Gbps/pino; para HBM4e, os fornecedores miram 1,6–2,0 TB/s por pilha, dependendo do clock e do número de camadas. Esse ganho vem acompanhado de PHYs otimizadas para acoplamentos curtíssimos (sub-1 mm) e separação de buses de dados e comando, reduzindo contenção e latências internas do subsistema.

Outro refinamento é a granularidade do acesso: mais subcanais independentes, que facilitam acessos concorrentes e melhoram a utilização sob cargas fragmentadas, em especial IA e HPC com padrões de acesso desbalanceados.

Eficiência energética e empilhamento 3D

O consumo por bit transferido é a régua que manda na memória de alto desempenho. A HBM3 gira em ~5–7 pJ/bit, enquanto a HBM4e promete cortes de 20–30% (faixa de ~3,5–5 pJ/bit) por meio de tensões menores, PHYs mais enxutas e gerenciamento dinâmico agressivo de energia.

Fabricantes também ventilam metas ainda mais ambiciosas quando a comparação é com HBM3E (~3,9 pJ/bit), sugerindo ganhos próximos a 2× em cenários-alvo. Na prática, espere reduções significativas no W/bit, especialmente valiosas em datacenters de IA com milhares de GPUs.

Na vertical, o salto vem do hybrid bonding (Cu–Cu), que substitui parte dos micro-bumps por conexões diretas de cobre. Isso derruba resistência e capacitância entre camadas, eleva a densidade de TSVs e viabiliza pilhas 16‑hi (ou mais) com melhor integridade elétrica e térmica. Técnicas como wafer-on-wafer (WoW) e die-to-wafer (D2W) pavimentam uma rota clara para HBM5 com empilhamentos ainda maiores.

Impacto em IA e HPC

- HPC: mais largura de banda por pilha reduz gargalos que travavam o escalonamento de aplicações vetorizadas e simulações de grande porte.

- IA: LLMs e modelos multimodais dependem de transferências maciças de pesos e gradientes; pilhas de 64–128 GB com alta taxa sustentada diminuem sharding entre GPUs.

- Eficiência: melhor desempenho por watt permite densidades maiores sem extrapolar envelopes térmicos do datacenter.

Para ampliar o contexto de hardware gráfico, vale conferir um guia das melhores placas de vídeo, especialmente se você compara cenários com GDDR e HBM em jogos e em aceleração de IA.

Fabricantes, metas e cronogramas

Os três grandes (Samsung, SK hynix e Micron) ditam o ritmo. Há um consenso de que a HBM4 deve iniciar produção em massa por volta de 2026, enquanto a HBM4e aparece na mira logo na sequência, com metas agressivas de performance.

No caso da Samsung, um anúncio feito no Open Compute Project Global Summit 2025 reforçou objetivos para a HBM4e: 3,25 TB/s por pilha, com pelo menos 13 Gbps por pino em uma interface de 2048 I/Os. Isso resulta em algo como 2,5× o throughput de HBM3E em configurações comparáveis.

A pressão vem de clientes como a NVIDIA (arquitetura Vera Rubin), que demandam taxas acima de 10–11 Gbps por pino. Em janeiro de 2025, na ISSCC em San Francisco, a Samsung elevou sua meta de HBM4 de 10 para 11 Gbps após pedidos de parceiros; a SK hynix acompanhou, e a Micron indicou amostras na faixa de 11 Gbps para avaliação.

Segundo as comunicações do setor, a SK hynix ocupa a liderança atual em HBM3E e foi indicada como a primeira a escalar HBM4 em volume, enquanto Samsung e Micron aceleram seus roadmaps. O mercado de HBM, impulsionado por IA/ML, pode superar a marca de US$ 100 bilhões até o fim da década.

Controlador integrado e funções “no pacote” na HBM4e

Uma iniciativa particularmente interessante vem da parceria SK hynix + TSMC, que busca integrar um controlador de memória junto às pilhas HBM4e. Com isso, funções de computação, cache e até recursos de memória em rede poderiam operar no próprio pacote, encurtando caminhos de dados e diminuindo consumo.

Essa abordagem “compute near memory” tem potencial para minimizar latências internas e reduzir o tráfego de ida e volta para logic dies distantes, trazendo ganhos em tarefas repetitivas ou filtragem/intermediação de dados antes de chegarem à GPU/ASIC.

HBM no PC? Por que a DDR5 ainda reina

Em tese, nada impede colar HBM a uma CPU mainstream ou até criar módulos dedicados. Na prática, os obstáculos de custo, capacidade e latência pesam, e as CPUs de desktop não precisam de um bus tão largo quanto GPUs e aceleradores.

- Custo: empilhamento 3D e interposers elevam o preço muito acima da DDR, sem retorno proporcional no desktop comum.

- Latência: para a CPU, latência baixa é crítica; a HBM tende a perder para DDR nesse quesito.

- Capacidade: a escalabilidade em GB por módulo é superior em DDR; HBM é limitada por altura de pilha e densidades dos dies.

- Termal/energia: pilhas densas aquecem mais; módulos HBM plugaram demandariam soluções térmicas ativas.

- Topologia: fora do mesmo pacote da CPU, distâncias maiores aumentam W/bit, anulando parte das vantagens.

Caso especiais existem: a Fujitsu A64FX usa HBM2 no lugar de RAM convencional, e houve implementações como Intel Xeon Phi (HCDRAM/Micron), Tesla P100 e NVIDIA Hopper GH100 com HBM. Para o desktop comum, DDR5 entrega o necessário; já em estações com muitos núcleos ou APUs com iGPU potente, o ganho de largura de banda poderia justificar estudos futuros.

DDR vs GDDR: diferenças essenciais

Apesar de compartilharem base tecnológica, DDR e GDDR divergem nas prioridades. DDR busca latência mínima e estabilidade com buses mais estreitos (p. ex., 128 bits entre CPU e RAM). GDDR privilegia throughput para atender o perfil de acesso massivamente paralelo das GPUs.

- DDR: foca em latência e eficiência com anchos modestos; exemplos típicos mostram ~88 GB/s em DDR5‑6400.

- GDDR: privilegia banda agregada; GDDR6 com buses de 384 bits em placas topo de linha alcança 1000+ GB/s (caso da RTX 4090: ~1008 GB/s).

No mundo dos SoCs, a Apple expandiu buses para escalar banda: M2 (128 bits), M2 Pro (256 bits), M2 Max (512 bits) e M2 Ultra (1024 bits, ~800 GB/s). Isso aproxima a largura de banda de GPUs, lembrando que CPU e GPU convivem no mesmo chip, encurtando caminhos.

GDDR7, GDDR6X e GDDR6W frente a HBM4/HBM4e

A GDDR7 chega para suceder a GDDR6, com até 32 Gbps por pino e ganhos de ~20% em eficiência. O salto vem com sinalização PAM3 e ajustes no encapsulamento que melhoram a resistência térmica em até ~70% versus a geração anterior.

Já a GDDR6X (Micron + NVIDIA) não é um padrão JEDEC e usa PAM4 para empurrar 19–21 Gbps por pino, superando a GDDR6 tradicional (até 16 Gbps/pino). A GDDR6W, por sua vez, dobra pinos de I/O (32 → 64), mira 22 Gbps/pino e duplica a densidade por chip (16 → 32 Gb), apertando ainda mais a disputa em banda efetiva por pacote.

Como fica frente a HBM? Em taxa por pino, GDDR6X/GDDR7 podem superar HBM4/HBM4e; porém, o bus HBM (2048 bits) é colossal, sustentando 1,6–2,0 TB/s por pilha e até 2,0+ TB/s no baseline HBM4 (8 Gbps/pino). Na prática, GDDR segue vencedora em custo por GB e flexibilidade em placas de vídeo, enquanto HBM domina onde throughput agregado e densidade por área são críticos.

HMC/HMC2: a alternativa que não vingou

Outra memória 3D de alto desempenho foi a HMC (Hybrid Memory Cube), da Micron em parceria com Samsung (2011). Ela prometia ordem de grandeza superior à DDR3 e trazia controlador integrado em um die lógico separado, com links seriais full‑duplex.

A primeira geração (HMC 1.0, 2013) oferecia links de 16 ou 18 lanes operando a 10/12,5/15 Gbps SerDes, somando ~40 GB/s por link (20 GB/s TX + 20 GB/s RX), com pacotes iniciais de 512 MB (~11 W a 1,2 V) e depois até 2 GB. A HMC2 (2014) elevou taxas para 12,5–30 Gbps, chegando a centenas de GB/s por link agregado. Ainda assim, a adoção foi limitada, e o projeto foi descontinuado em 2018.

Houve casos notáveis como o Fujitsu SPARC64 XIfx (supercomputador PRIMEHPC FX100, 2015), mas o mercado rapidamente convergiu para HBM e GDDR, que mostraram maior tração industrial e ecossistema de suporte.

Detalhes JEDEC HBM4 que fundamentam a HBM4e

A especificação HBM4 do JEDEC estabelece a base sobre a qual a HBM4e se estende. Interface de 2048 bits com 32 canais (64 pseudo‑canais), densidades de 24/32 Gb por die e pilhas até 16‑hi conferem banda de até 2 TB/s a 8 Gbps/pino.

Os documentos também mencionam tensões VDDQ de 0,7–0,9 V e VDDC de 1,0–1,05 V, separação de buses de dados/comandos para reduzir latência interna, DRFM (Directed Refresh Management) para mitigar row‑hammer e recursos de RAS/diagnóstico reforçados – todos pilares que a HBM4e aproveita e expande com clocks e PHYs mais agressivos.

Mercado, IA e outras frentes tecnológicas

Além da HBM, fornecedores como a Samsung detalharam avanços paralelos: LPDDR6 próxima de 10,7 Gbps/pino (~114,1 GB/s) com +20% em eficiência face à LPDDR5X, além de nós lógicos de 2 nm (SF2) com produção prevista para o fim de 2025.

Também surgem colaborações curiosas, como a Rebel‑CPU (em parceria com a Rebellions), combinando SF2 e SF4X em projetos que apontam para heterogeneidade e empacotamento avançado. O fio condutor é evidente: IA escala mais rápido do que a memória tradicional consegue acompanhar, e empurrar a computação para perto (ou dentro) da memória ajuda.

Relatos do setor citam ainda vazamentos e exclusivas em redes como o X dando conta do ritmo de amostras e metas internas, especialmente quando grandes clientes pressionam por saltos rápidos de velocidade por pino e por pilha.

Por fim, vale relembrar que os grandes aceleradores de IA como NVIDIA Blackwell, AMD Instinct e ASICs de Google/Amazon dependem diretamente de escolhas de memória. A chegada de HBM4/HBM4e define capacidades de treino e inferência de toda uma geração de hardware.

Com tudo isso, a HBM segue como a preferida dos hiperescaladores, ao mesmo tempo em que enfrenta barreiras conhecidas fora do nicho: custo elevado do empacote 3D e desafios térmicos inerentes a pilhas altas e clocks crescentes. A indústria já investiga materiais, interfaces e topologias alternativas para tornar a HBM mais acessível; se isso acontecer, ela pode avançar para além do HPC/IA e disputar espaço em mais frentes.

No estado atual, a fotografia é clara: HBM4e promete dobrar o fôlego da memória de alto desempenho com bus de 2048 bits, taxas que podem passar de 12 Gbps/pino e eficiência melhor, enquanto GDDR7/GDDR6X/GDDR6W mantêm a hegemonia em placas de vídeo pelo custo e flexibilidade. A escolha certa dependerá do equilíbrio entre banda, latência, capacidade, consumo e preço em cada caso de uso.